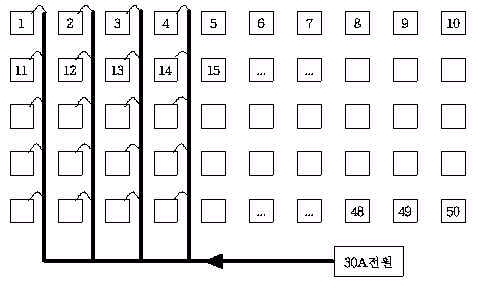

DOT MATRIX MODULE 과 전원

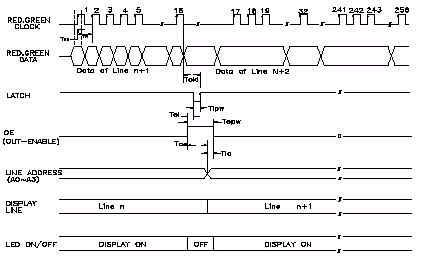

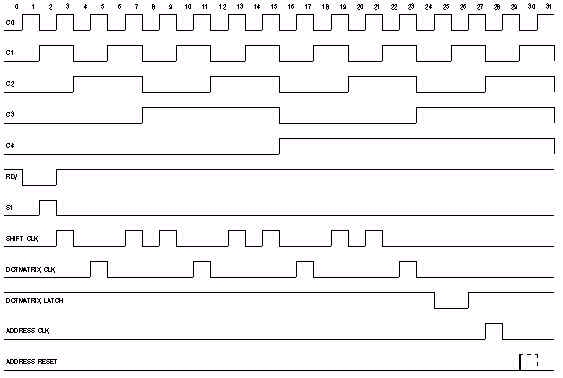

[그림4.5] LED Module의 Timing chart

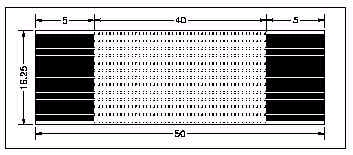

MATRIX MODULE 연결 CABLE

[그림 5] 연결 케이블

[그림6] 케이블 연결도

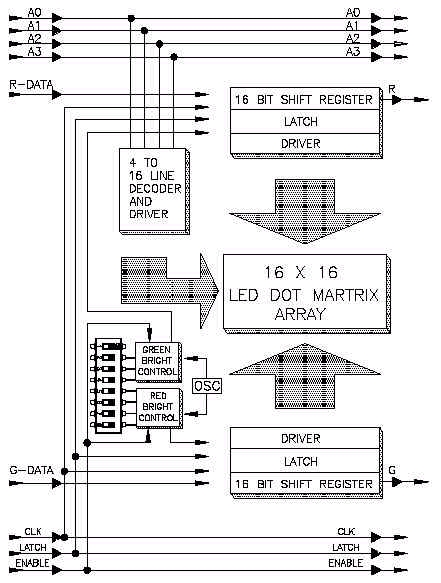

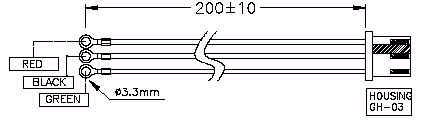

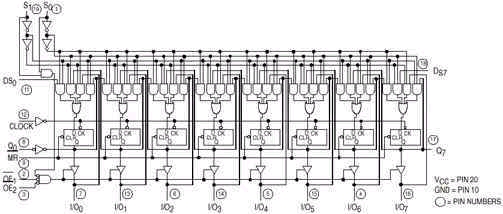

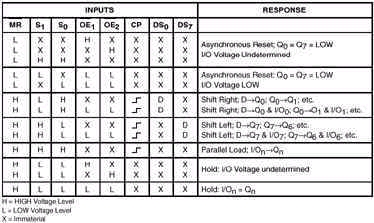

SHIFT REGISTER

[그림8] shift register

[그림9] truth table

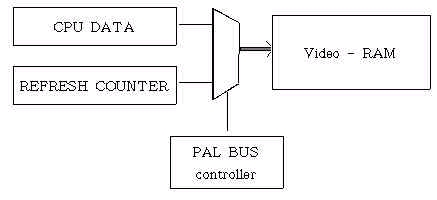

BUS DRIVER - MUX

CLOCK-GENERATOR Timing Chart

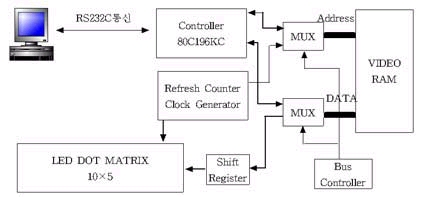

CPU module

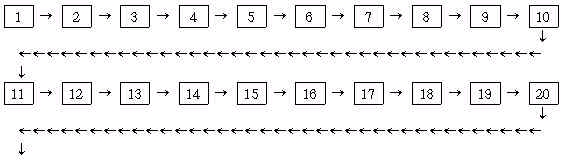

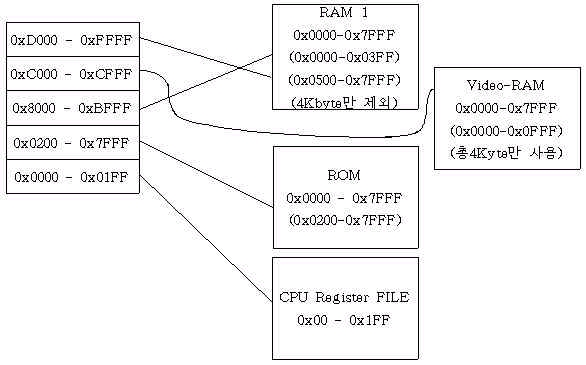

[그림 ] memory map 에디터 만들기 4가지 색만을(검정,초록,빨강,분홍) 표현할 수 있기때문에 사진을 바로 전광판에 출력할 수 는 없다. 따라서 비슷한 색으로 바꿔주는 기능이 필요하며, 에니메이션을 효과를 넣기 위해서 여러장의 그림을 편집할 수 있는 기능이 필요하다. 데이터는 시리얼 통신을 통해서 콘트롤러에 들어가며 콘트롤러는 수신된 데이터를 비디오램 또는 데이터공간 어디에든 저장할 수 있다. 이미지 한장은 4Kbyte를 차지하므로 32Kbyte의 RAM공간에서 실제로 사용할 수 있는 장수는 4~5장 정도 이다. 하지만 시리얼 통신이 115200bps로 비교적 고속이기 때문에 OnLine으로 화면을 업데이트 시켜도 보는데 큰 지장은 없다. |

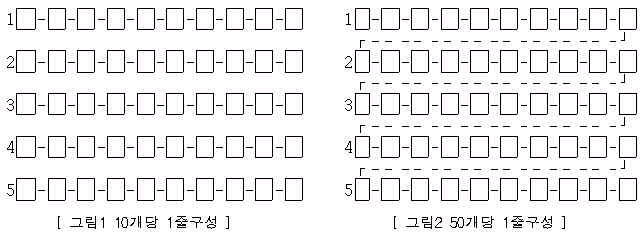

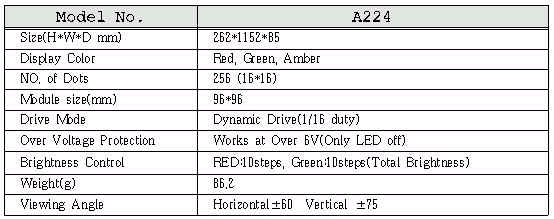

Dynamic Drive Type LED Matrix Module 전광판 설명 및 도면

조회 1,142

작성 2020. 11. 27. 18:29:34

fileAttachedList

15

474cf9687e3a3.jpg

(19.97kB)

474cf9efe0ba5.jpg

(54.46kB)

474cf9687e3a3.jpg

(19.97kB)

474cf854a7e8f.jpg

(30.19kB)

474cf8f5794ea.jpg

(31.64kB)

474cf9bcf3f16.jpg

(43.53kB)

474cfa22e48ea.jpg

(48.28kB)

474cf9d7a9053.jpg

(56.19kB)

474cf8be744fc.jfif

(58.33kB)

474cfa41336d0.jpg

(62.46kB)

474cf8947c7f0.jpg

(97.73kB)

474cfa0fcb328.jpg

(17.62kB)

474cf8dc1d8de.jpg

(40.42kB)

474cf81d1d974.jpg

(70.21kB)

474cf99d070f8.jpg

(35.02kB)

0개 댓글